仔細講一下 Data_Previous1 <= Data1;

我們來寫個範例

設計上來講就是一個

輸出 Out1<=Date;

module Clk_Add1(reset1,Date,clk,Out1);

input reset1 ,clk;

input [7:0] Date;

output[7:0] Out1;

reg[7:0] Out1;

always@(negedge reset1 or posedge clk)

begin

if( ~reset1) begin

Out1<=0;

end

else begin

Out1<=Date;

end

end

endmodule

tb

一開始 reset 開啟之後,每到一個

posedge clk 就是 clk 到 High

設定上:

always #10 Date<=~Date;

always #5 clk<=~clk;

module tb1();

reg reset1 ,clk ;

reg Date;

wire Out1;

Clk_Add1 Clk_test(.reset1(reset1), .Date(Date) ,.clk(clk),.Out1(Out1));

initial begin

clk<=0;reset1<=0;Date<=0;

#7 reset1<=1;

#6000 $stop;

end

always #10 Date<=~Date;

always #5 clk<=~clk;

endmodule

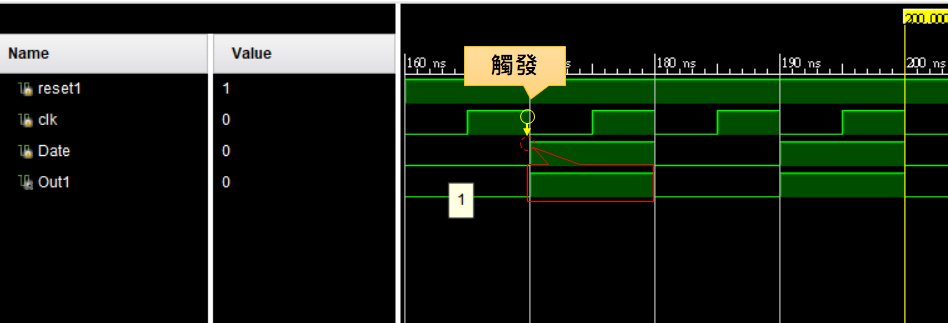

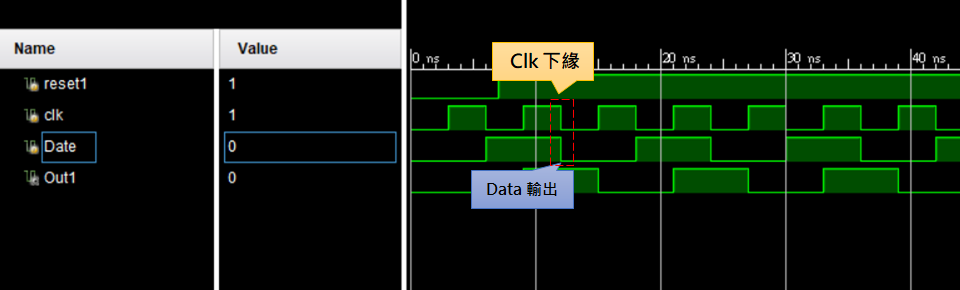

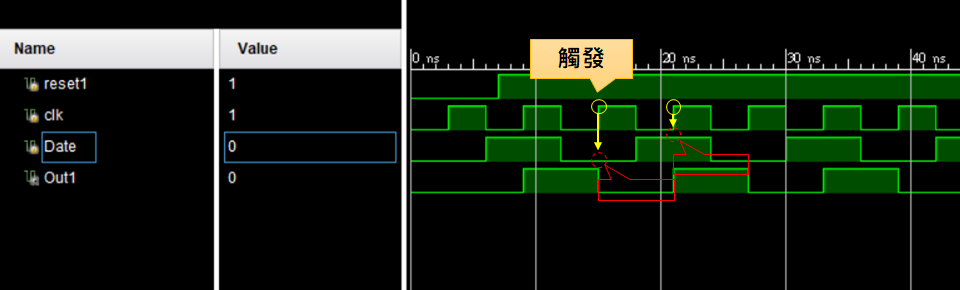

有注意到嗎? 我們是設定的是 Clk跟 DATA是對到的

所以 Clk 下緣 → Data 輸出

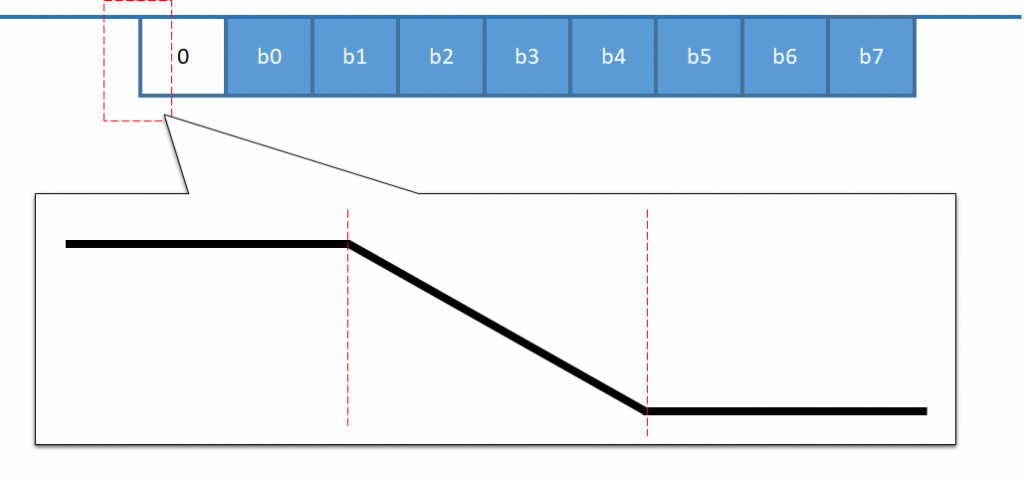

然後我們的觸發是 Clk的上緣,那我們拿到的 Data 就是上一筆的中間

所以在這個案例中posedge clk 配合 Out1<=Date; 就是上一筆的中間

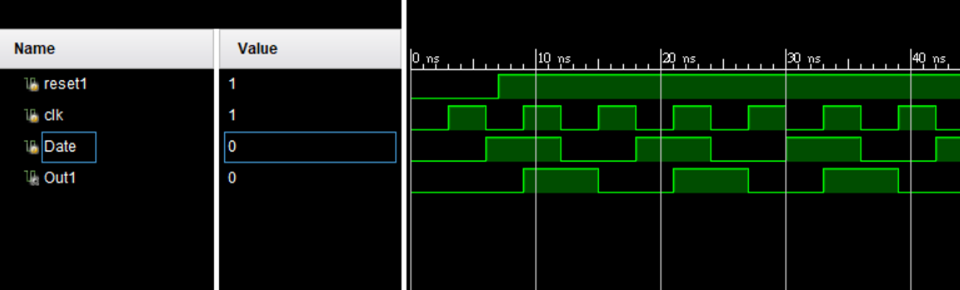

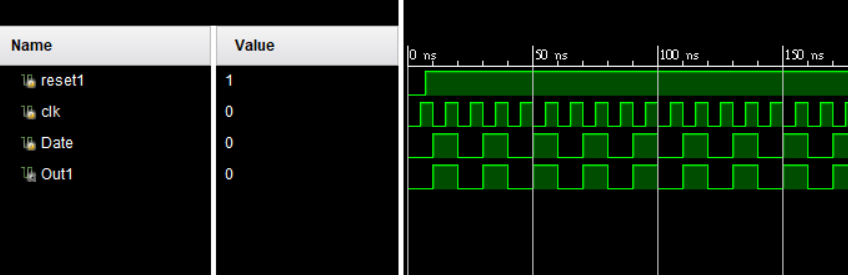

我們假設 設定成 negedge clk 配合 Out1<=Date;

module Clk_Add1(reset1,Date,clk,Out1);

input reset1 ,clk;

input Date;

output Out1;

reg Out1;

always@(negedge reset1 or negedge clk)

begin

if( ~reset1) begin

Out1<=0;

end

else begin

Out1<=Date;

end

end

endmodule

tb

module tb1();

reg reset1 ,clk ;

reg Date;

wire Out1;

Clk_Add1 Clk_test(.reset1(reset1), .Date(Date) ,.clk(clk),.Out1(Out1));

initial begin

clk<=0;reset1<=0;Date<=0;

#7 reset1<=1;

#6000 $stop;

end

always #10 Date<=~Date;

always #5 clk<=~clk;

endmodule

結果如下

觸發在 clk下緣,那 Data 剛好發射,那就是同步了